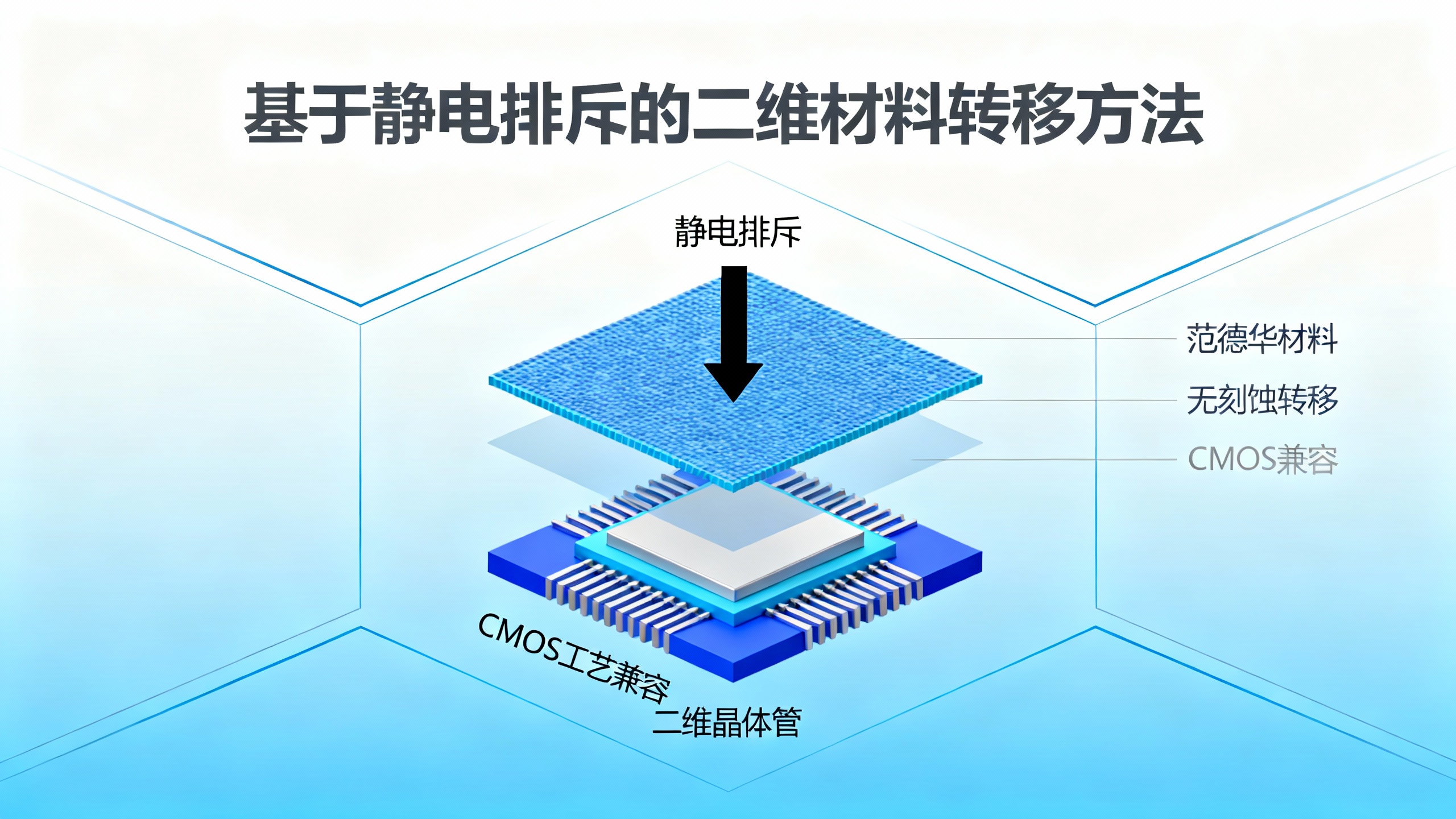

静电排斥一步搞定!范德华材料“无损大挪移”术,让2D芯片卷进3D时代

作者: aeks | 发布时间: 2025-10-04 22:32 | 更新时间: 2025-10-04 22:32

把2D材料从生长衬底“搬家”到目标芯片,就像把一张超薄宣纸从玻璃板上揭下来——一撕就破、一碰就皱,还沾满“前任”残渣。传统湿法腐蚀像用强酸洗锅,干净但会把锅洗漏;干法剥离又像用胶带粘画,快却难免留痕。今天这篇Nature直接甩出王炸:用氨水电场双电层(EDL)静电排斥,秒撕不留痕,100%完整率,晶圆级尺寸,成本低到白菜!

我连夜读完,把硬核论文翻译成菜市场能听懂的大白话,顺带拆成三步“懒人包”:

1️⃣ 氨水=“卸妆水”

32 wt%浓氨水一泡,MoS₂和蓝宝石衬底瞬间“感情破裂”。DLVO理论算得明明白白:pH 12时表面电荷同号,静电排斥力≈“前任拉黑”,材料自己“跳”下来,全程零腐蚀,连SiO₂衬底泡100小时都没掉皮。

2️⃣ 铋金属=“黄金CP”

转完不是终点,还要“无缝入住”。团队用铋(Bi)做接触电极,把MoS₂晶体管的开电流推到1.3 mA/μm@1 V,比传统Ti/Au高3倍,亚阈值摆幅65.9 mV/dec,接近理论极限,直接刷新2D晶体管天花板。

3️⃣ 晶圆级=“批量印钞”

2英寸MoS₂薄膜完整转移,100%器件良率,短沟道25 nm器件开态电流48.4 μA/μm,甩KOH法十条街。石墨烯、WSe₂、CNT全通杀,甚至能多层堆叠,3D集成像叠乐高。

一句话总结:以后做柔性屏、脑机接口、量子芯片,再也不用“小心翼翼”地抠材料,直接氨水一泡,静电一弹,2D材料乖乖就位。CMOS产线今天就能用,成本低到老板笑出鹅叫。

论文指路👉Nature 645, 906–914 (2025) DOI: 10.1038/s41586-025-09510-0