300 mm晶圆厂也能做出99%+保真度的硅自旋量子比特!实验室神话正式落地工业线

作者: aeks | 发布时间: 2025-10-04 22:32 | 更新时间: 2025-10-04 22:32

学科分类: 信息与通信工程 控制科学与工程 电子科学与技术 计算机科学与技术

正文:

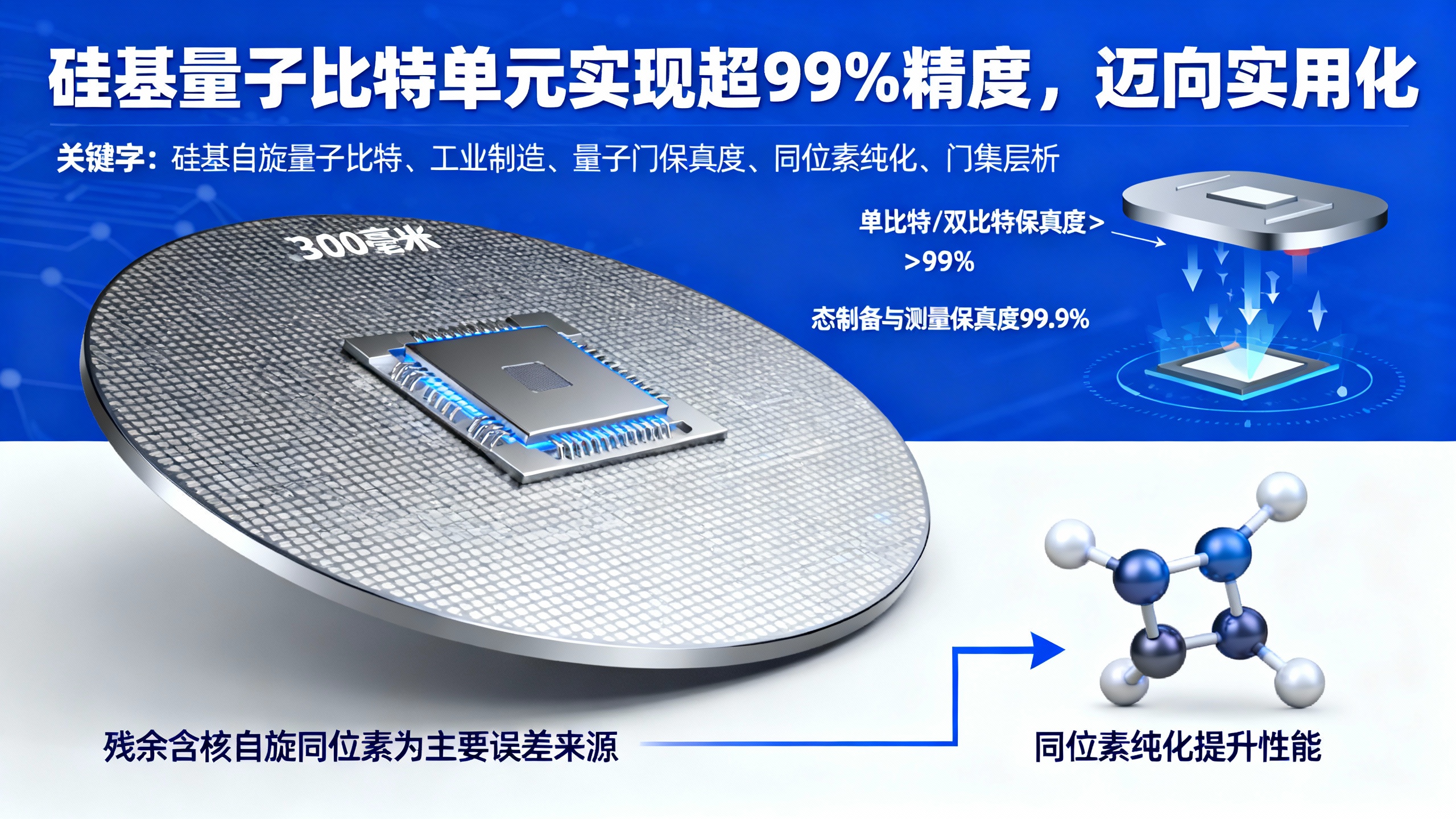

先放结论:Diraq×imec联合团队在最新一期Nature发文,用标准300 mm CMOS工艺流片出的硅自旋量子比特单元,单/双比特门保真度全部≥99%,SPAM(状态制备+读出)直接飙到99.95%。一句话——实验室里吹的牛,晶圆厂真的做到了。

🌟 为什么说这次不一样?

- 过去担心工业线噪声大、缺陷多,做不出学术圈的高保真度。这回直接在imec 300 mm pilot line里用“老古董”平面MOS+多晶硅栅结构,四颗芯片全部达标。

- 单比特T1最长9.5 s,Hahn回波T2达1.9 ms,Ramsey T2*≈40 μs——跟学术小批量器件一个量级。

- 用gate set tomography(GST)把误差拆成“谁拖了后腿”:主要是残余²⁹Si核自旋噪声,也就是材料里天然硅同位素惹的祸。→ 解决方案简单粗暴:继续提纯硅,把²⁹Si从400 ppm降到50 ppm以下,就能再涨一波性能。

🔬 实测数据速览(四颗芯片汇总)

| 指标 | 最小值 | 最大值 |

|---|---|---|

| 单比特门保真度 | 99.23% | 99.64% |

| 双比特CZ门保真度 | 99.04% | 99.56% |

| SPAM保真度 | 99.33% | 99.96% |

🛠️ 工艺细节一句话总结

- 衬底:同位素富集硅(²⁹Si 400 ppm)+热氧化SiO₂界面,保证低电荷噪声。

- 栅极:三层叠栅,电子束光刻+干法刻蚀,栅间距<100 nm,完全兼容CMOS。

- 读出面:单电子晶体管(SET) d.c.读出,未来可升级低温放大器提速。

📈 下一步?

1. 硅片级统计:目前手动校准太费劲,得把自动化流程跑通。

2. 同位素再提纯:²⁹Si降到50 ppm以下,预计能把保真度再抬0.1~0.2%。

3. 全局微波+高温场景:模拟CMOS芯片上集成控制电子后的真实工作环境。

一句话总结:硅自旋量子比特终于拿到“工业级入场券”,大规模量子计算离我们又近了一大步。